概 要

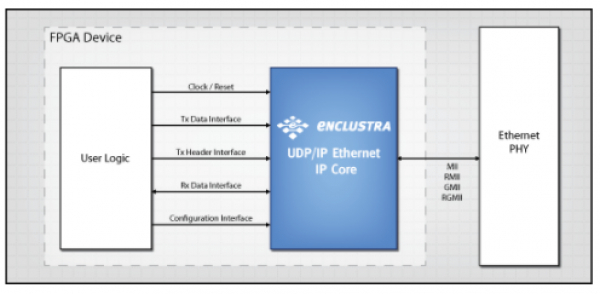

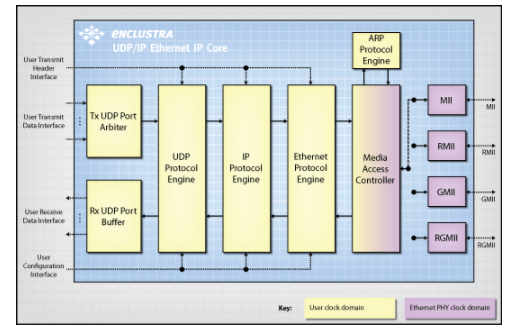

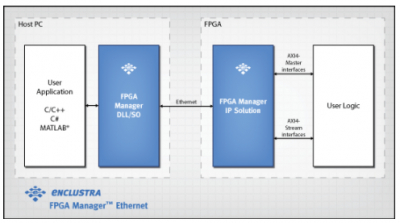

ユーザーロジックへのインターフェイスを使用するのが簡単で、一般的なメディアに依存しないインターフェイスMII、RMII、GMII、およびRGMIIをサポートします。125MHzで動作する8ビット幅の送受信インタフェースにより、IPコアは1Gbit / secの完全なワイヤ速度で動作することができます。100 Mbit / secおよび10 Mbit / secの動作もサポートされています。

ハイライト

・ 全1Gbit / secのワイヤスピードで動作

・ 完全なUDP、IPv4、およびEthernetレイヤ処理

・ 自動ARP応答の生成

・ ヘッダーパススルーモード:

- デフォルトのUDP / IP / ETHヘッダーフィールド値を送信データストリームに埋め込まれた値で選択的に上書き

- UDP / IP / ETHヘッダフィールド値を受信データストリームに選択的に埋め込み、ユーザアプリケーションへの配信を容易

利 点

・ FPGAベースのシステムとの標準UDP通信

・ フル1Gbit / secのワイヤスピードを実現

・ 低いFPGAリソース使用率

特 徴

・ Gビット/秒、100Mビット/秒、10Mビット/秒の動作

・ MII、RMII、GMIIおよびRGMIIメディア独立インタフェース(全二重のみ)

・ 宛先UDPポート、宛先IPアドレス、および宛先MACアドレスフィルタリング

・ UDPチェックサムの計算とチェック

・ イーサネットフレームチェック

・ ポートごとに専用の受信および送信インターフェイスを備えた複数のUDPポート

・ オプションの受信データバッファ

・ 非UDP通信用の未処理のイーサネットポート

ご提供

・ UDP / IPイーサネットIPコア

- VHDLソースファイル(製品オプションに応じてプレーンまたは暗号化)

- リファレンスデザイン

- ユーザーマニュアル

・ UDP / IPイーサネットIPコアリファレンスデザイン

- リファレンスデザインのトップレベルVHDLファイル(プレーンVHDL)

- UCF / XDC / SDC制約ファイル(製品オプションによる)

- ザイリンクスISE /ザイリンクスVivado™/インテル®Quartus®プロジェクトファイル(製品オプションに依存)

- トップレベルのシミュレーションテストベンチファイル(プレーンVHDL)

- トップレベルシミュレーションModelSimプロジェクトファイル

- ドキュメンテーション